- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

- Tablero central

- Tablero industrial

- Tablero portador del kit de desarrollo

- Placa portadora del kit de desarrollo PX30

- Placa portadora del kit de desarrollo RK3399

- Tablero portador del kit de desarrollo RV1126

- Placa portadora del kit de desarrollo RK3568

- Placa portadora del kit de desarrollo RK3566

- Placa portadora del kit de desarrollo RK3588

- Tablero de operadores de kit de desarrollo RK3562

- Computadora integrada

- Accesorios

- Bloqueo inteligente

- Computadora de tablas individuales

- Tienes poco

Placa de desarrollo RK3568

RK3568, el procesador Cortex-A55 de cuatro núcleos y 64 bits, con proceso de litografía de 22 nm, tiene una frecuencia de hasta 2,0 GHz, lo que brinda un rendimiento eficiente y estable para el procesamiento de datos de equipos de back-end. Hay una variedad de opciones de almacenamiento, lo que permite a los clientes implementar rápidamente la investigación y producción de productos. Admite hasta 8 GB de RAM, con un ancho de hasta 32 bits y una frecuencia de hasta 1600 MHz. Es compatible con ECC de enlace de datos, lo que hace que los datos sean más seguros y confiables, y cumple con los requisitos para ejecutar aplicaciones de productos de memoria grande. Está integrado con GPU de doble núcleo, VPU de alto rendimiento y NPU de alta eficiencia. La GPU es compatible con OpenGL ES3.2/2.0/1.1, Vulkan1.1. La VPU puede lograr decodificación de video 4K 60fps H.265/H.264/VP9 y codificación de video 1080P 100fps H.265/H.264. La NPU admite el cambio con un solo clic de marcos convencionales como Caffe/TensorFlow.

Enviar Consulta Descargar PDF

Thinkcore TC-RK3568 Especificación de placa de desarrollo de orificio de sello

Declaración de derechos de autor

Los derechos de autor de este manual pertenecen a Shenzhen Thinkcore Technology Co., Ltd. y todos los derechos están reservados. Ninguna empresa o individuo puede extraer parte o la totalidad de este manual, y los infractores serán procesados conforme a la ley.

Atención:

Los manuales de la plataforma de desarrollo en venta se actualizarán de vez en cuando, descargue el manual más reciente del sitio web www.think-core.com o comuníquese con el representante de ventas de nuestra compañía, no habrá más avisos.

Nota de lanzamiento

|

Versión |

Fecha |

Autor |

Descripción |

|

Rev.01 |

2022-08-04 |

|

Revisión |

Capítulo 1. Introducción a la placa de desarrollo de orificio de sello TC-RK3568

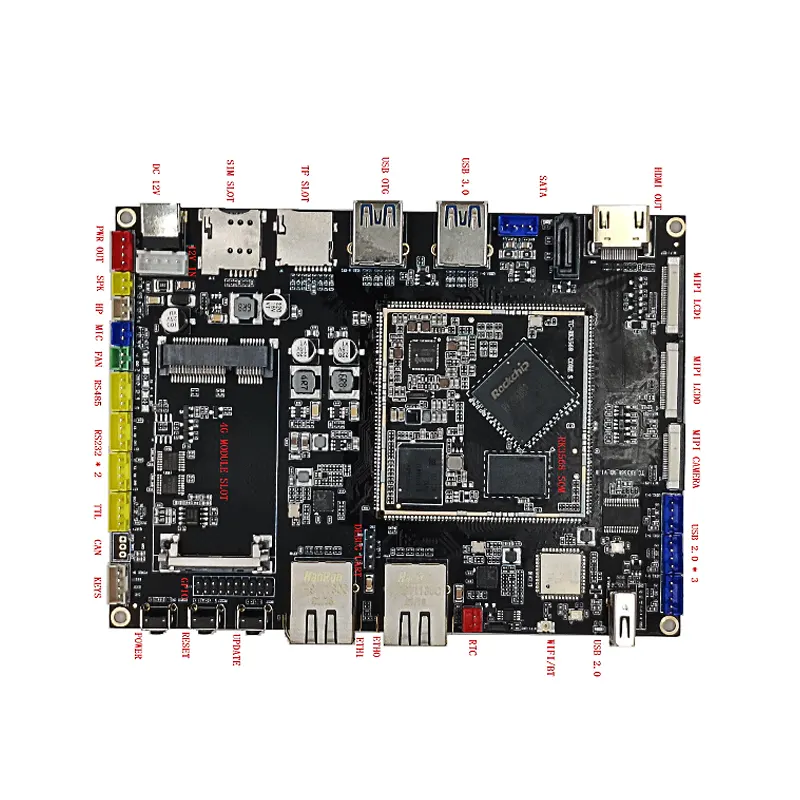

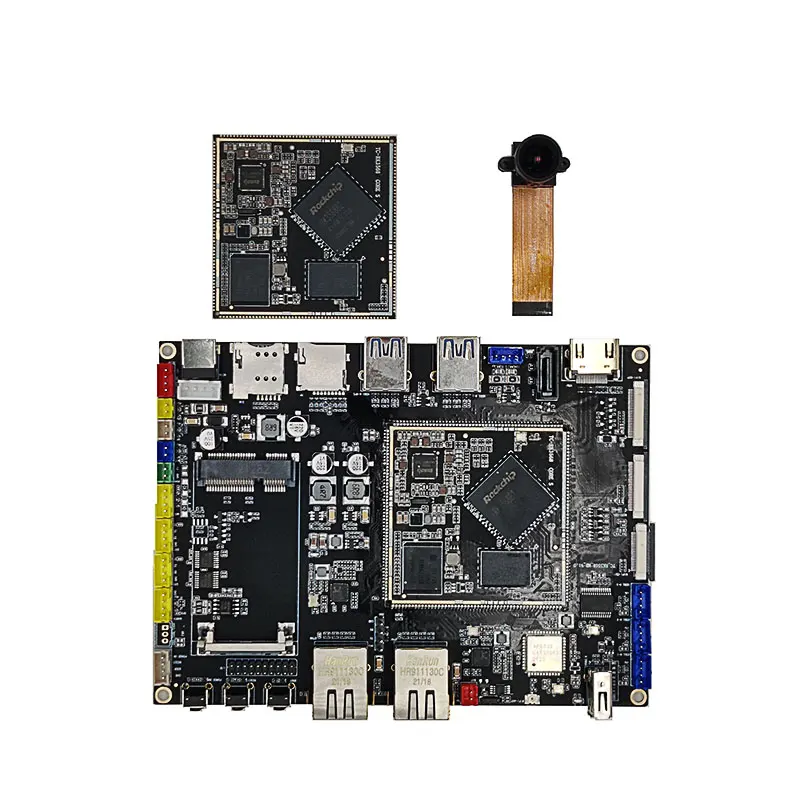

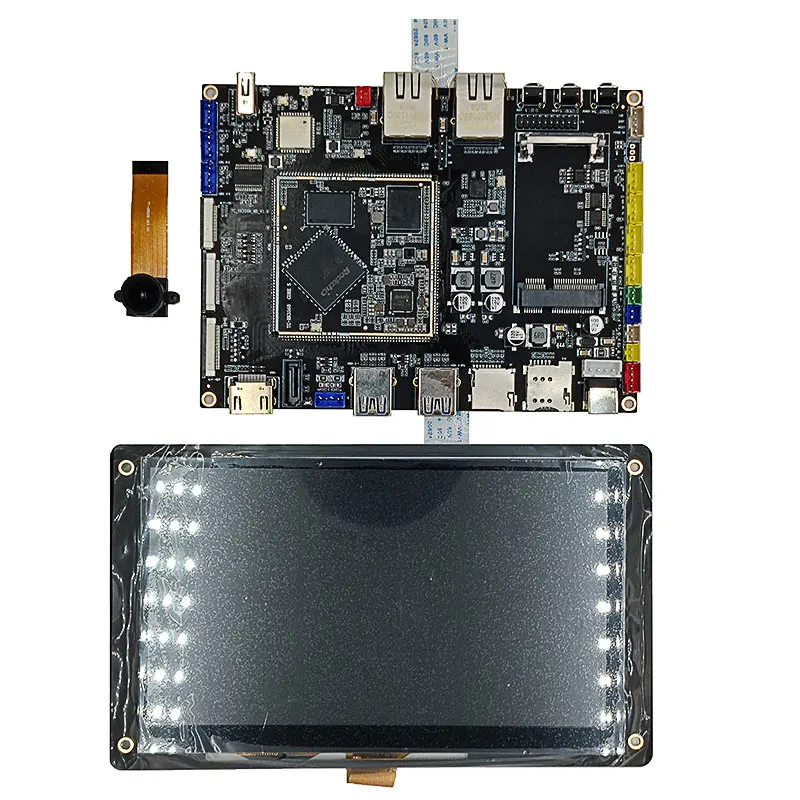

Resumen de la placa de desarrollo de agujeros de sello TC-RK3568

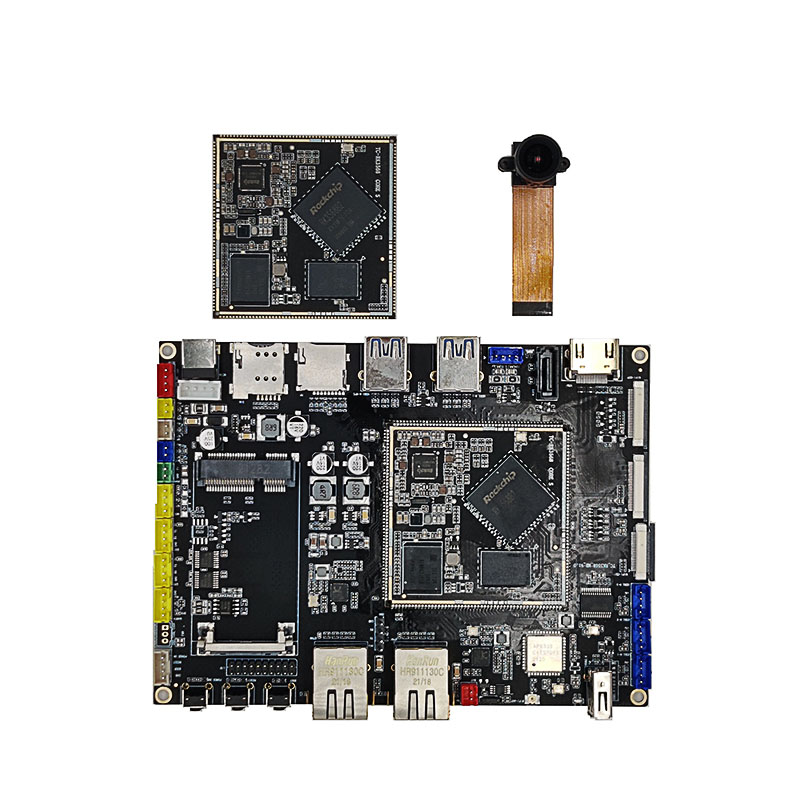

La placa de desarrollo de orificio de sello TC-RK3568 incluye SOM de orificio de sello TC-RK3568 y placa portadora.

El sistema TC-RK3568 Stamp Hole en el módulo está equipado con el procesador Rockchip RK3568 de 64 bits que está configurado con GPU de doble núcleo y NPU de alto rendimiento.

RK3568, el procesador Cortex-A55 de cuatro núcleos y 64 bits, con proceso de litografía de 22 nm, tiene una frecuencia de hasta 2,0 GHz, lo que brinda un rendimiento eficiente y estable para el procesamiento de datos de equipos de back-end. Hay una variedad de opciones de almacenamiento, lo que permite a los clientes implementar rápidamente la investigación y producción de productos. Admite hasta 8 GB de RAM, con un ancho de hasta 32 bits y una frecuencia de hasta 1600 MHz. Es compatible con ECC de enlace de datos, lo que hace que los datos sean más seguros y confiables, y cumple con los requisitos para ejecutar aplicaciones de productos de memoria grande. Está integrado con GPU de doble núcleo, VPU de alto rendimiento y NPU de alta eficiencia. La GPU es compatible con OpenGL ES3.2/2.0/1.1, Vulkan1.1. La VPU puede lograr decodificación de video 4K 60fps H.265/H.264/VP9 y codificación de video 1080P 100fps H.265/H.264. La NPU admite el cambio con un solo clic de marcos convencionales como Caffe/TensorFlow.

Con las interfaces de video MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, EDP, puede admitir hasta tres salidas de pantalla con diferentes pantallas. El ISP 8M incorporado admite cámaras duales y HDR. La interfaz de entrada de video se puede conectar a una cámara externa o a varias cámaras. Está equipado con dos puertos RJ45 Gigabit Ethernet adaptables, a través de los cuales se puede acceder y transmitir datos de red internos y externos, mejorando la eficiencia de transmisión de la red y satisfaciendo las necesidades de productos con múltiples puertos de red como NVR y gateway industrial.

La placa portadora incluye muchas interfaces, como puerto 4G LTE, USB3.0, USB2.0, PCIE, Ethernet dual, WIFI, Bluetooth, entrada y salida de audio, salida HDMI, pantalla MIPI DSI, pantalla eDP, pantalla LVDS, MIPI CSI cámara, ranura para tarjeta TF, RS485, RS232, TTL, CAN, Power out, SATA, etc.

Se admiten Android 11, sistema operativo Ubuntu 18.04, sistema operativo Debian y Linux Buildroot. La operación estable y confiable proporciona un entorno de sistema seguro y estable para la investigación y producción de productos.

Se proporciona un SDK completo, documentos de desarrollo, ejemplos, documentos de tecnología, tutoriales y otros recursos para que los usuarios realicen una mayor personalización.

Características de la placa de desarrollo de orificio de sello TC-RK3568:

Tamaño: 150 mm x 110 mm.

Las interfaces ricas se pueden usar directamente en varios productos inteligentes para facilitar la finalización de los productos.

Se admiten Android 11.0, Ubuntu 18.04 OS, Debian OS y Linux Buildroot.

Solicitud

Esta placa se puede usar ampliamente en NVR inteligentes, terminales en la nube, puertas de enlace IoT, control industrial, computación de borde, puertas de reconocimiento facial, NAS, consolas centrales de vehículos, etc.

Parámetro característico

|

Especificaciones |

|

|

UPC |

RockChip RK3568, Cortex-A55 de 64 bits de cuatro núcleos, proceso de litografía de 22 nm, frecuencia de hasta 2,0 GHz |

|

GPU |

BRAZO G52 2EE Admite OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Hardware de aceleración 2D de alto rendimiento integrado |

|

NPU |

0.8Tops@INT8, acelerador de IA integrado de alto rendimiento RKNN NPU Admite el cambio con un solo clic de Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

VPU |

Admite decodificación de video 4K 60fps H.265/H.264/VP9 Soporta codificación de video 1080P 100fps H.265/H.264 Soporta 8M ISP, soporta HDR |

|

RAM |

2GB/4GB/8GB |

|

Almacenamiento |

eMMC de 8GB/16GB/32GB/64GB/128GB Admite SATA 3.0 x 1 (expandible con SSD/HDD de 2,5â) Admite ranura para tarjeta TF x1 (expandir con tarjeta TF) |

|

SO del sistema |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Características del hardware |

|

|

Mostrar |

1 * HDMI2.0, admite salida 4K @ 60fps 1 * MIPI DSI, admite salida de 1920*1080@60fps 1 * LVDS, admite salida de 1920*1080@60fps 1 * eDP1.3, admite salida de 2560x1600 @ 60fps |

|

ethernet |

Admite dos puertos Gigabit Ethernet (1000 Mbps) |

|

Wifi |

Mini PCIe para conectar 4G LTE Soporta Wi-Fi 6 (802.11 AX) Soporta BT5.0 |

|

PCIE3.0 |

Soporta interfaz PCE3.0 |

|

Audio |

1 * salida de audio HDMI 1 * salida de altavoz 1 * salida de auriculares 1 * entrada de audio integrada de micrófono |

|

Cámara |

Admite interfaz de cámara MIPI-CSI de 1 canal Admite HDR, la imagen permanece clara con luz de fondo o condiciones de luz intensa

|

|

USB |

1 * Anfitrión USB 3.0, 4 * Anfitrión USB 2.0, 1 * USB 3.0 OTG |

|

sata |

1 * SATA, 6,0 Gb/s |

|

De serie |

1 * TTL, 2 * RS232, 1 * RS485 |

|

PUEDE |

Compatible con CAN2.0B, compatible con 1Mbps, 8Mbps |

|

Tarjeta TF |

1 * ranura para tarjeta TF |

|

Otros |

GPIO y ADC |

|

Tamaño |

150 mm * 110 mm |

|

|

|

|

Voltaje de entrada |

12V/3A |

|

Temperatura de almacenamiento

|

-30~80â |

|

Temperatura de funcionamiento |

-20~60â |

|

Humedad de almacenamiento |

10%~80% |

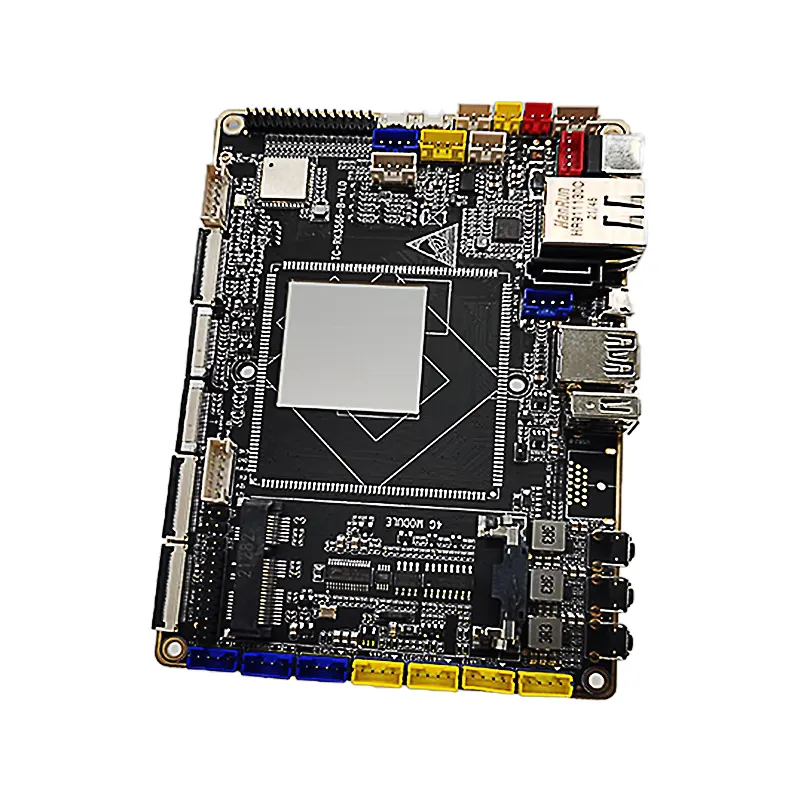

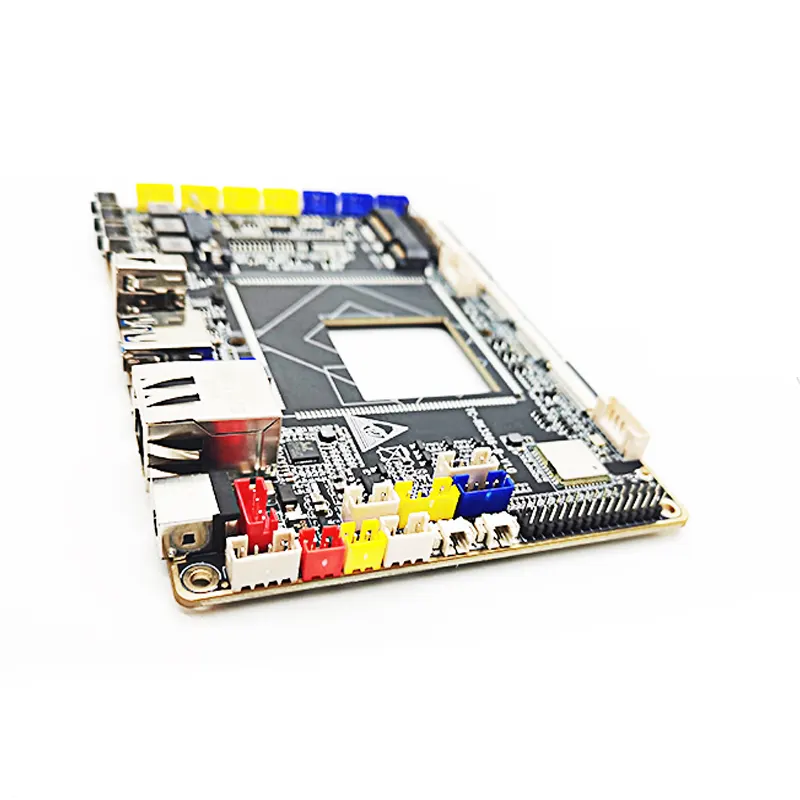

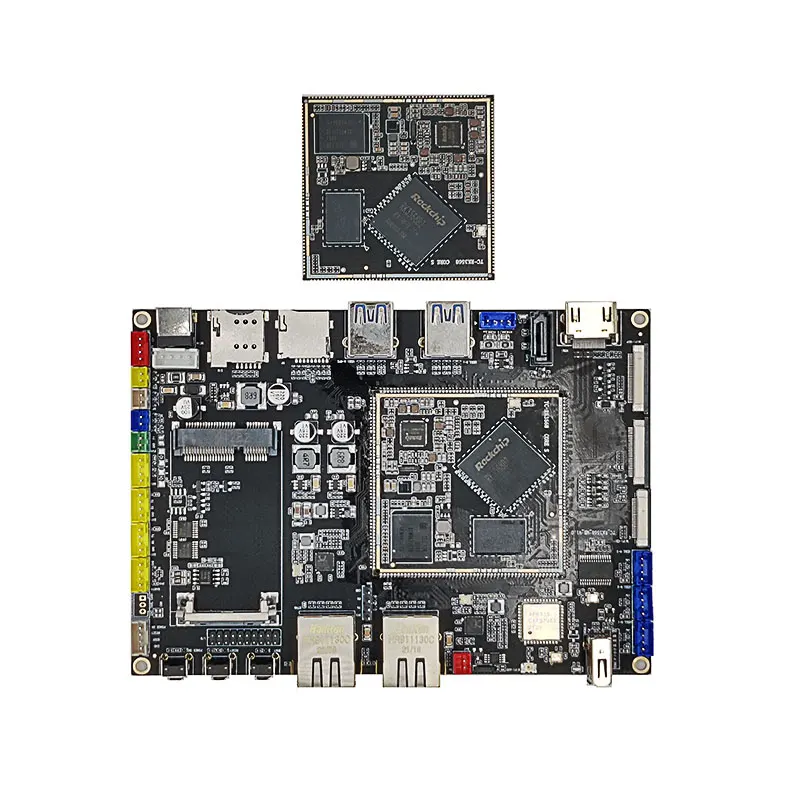

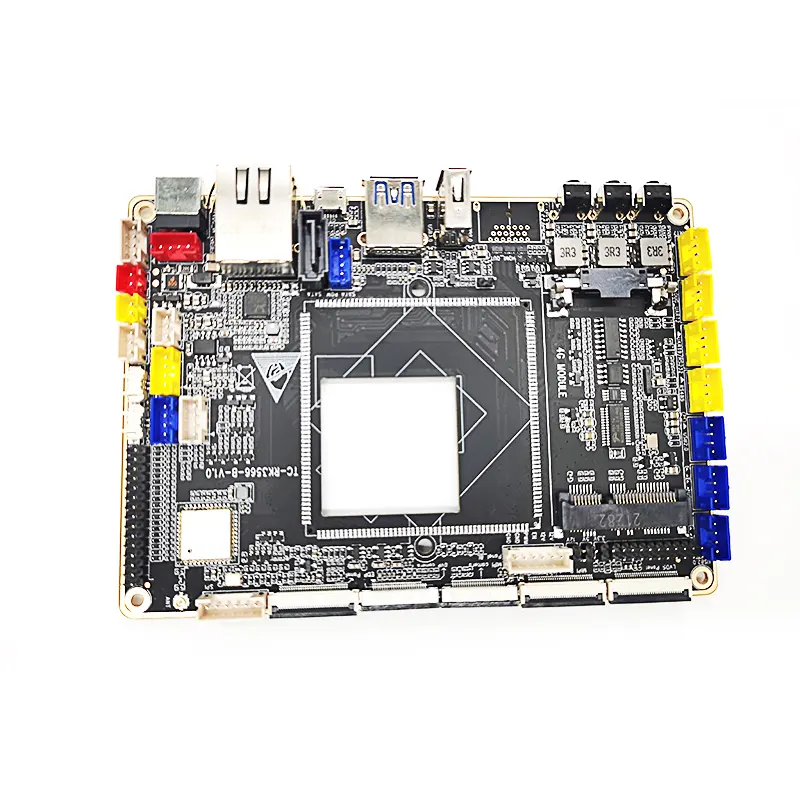

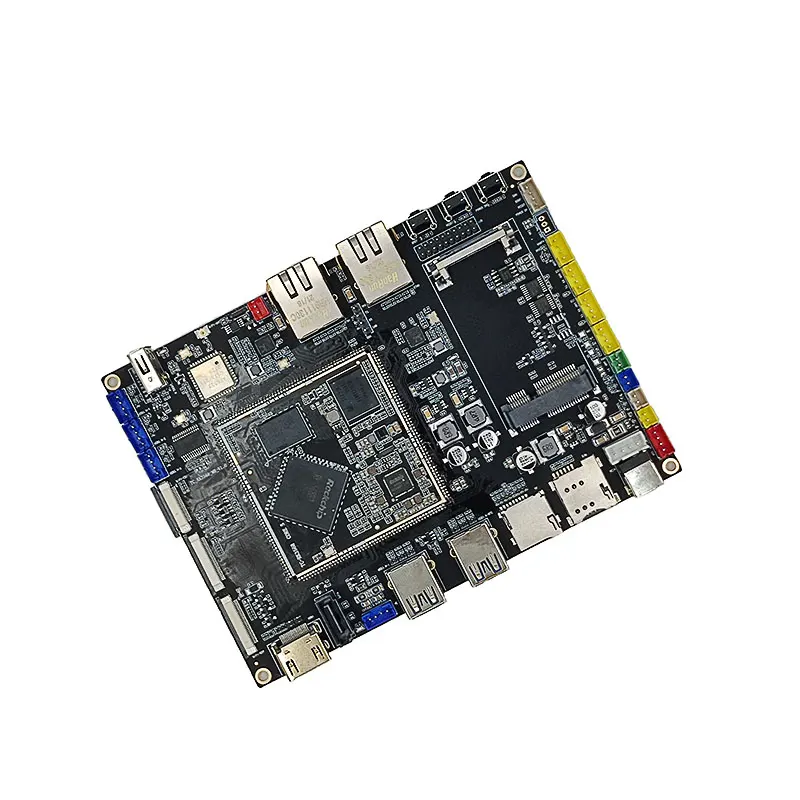

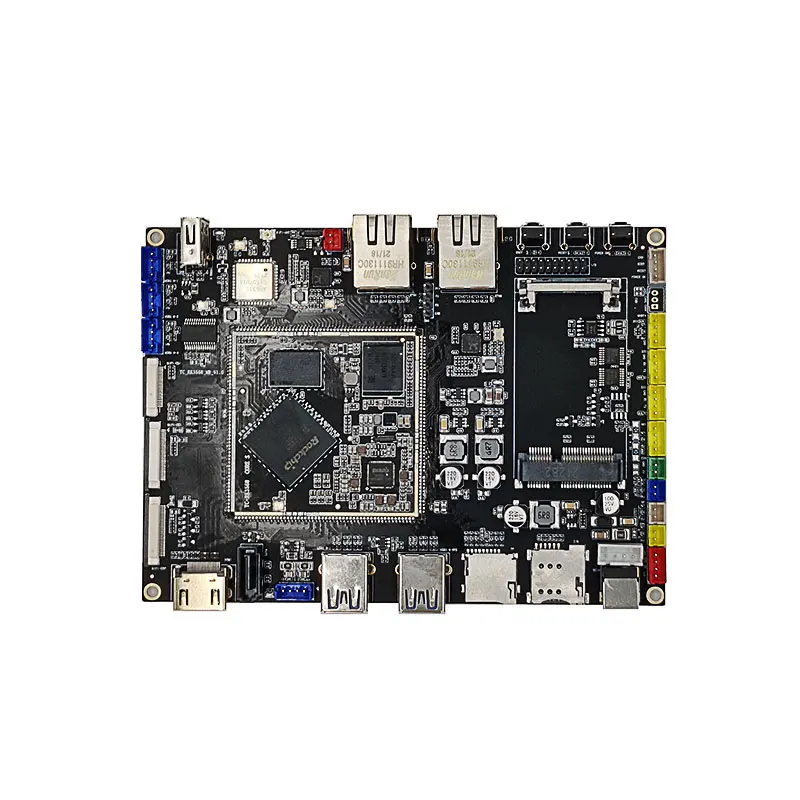

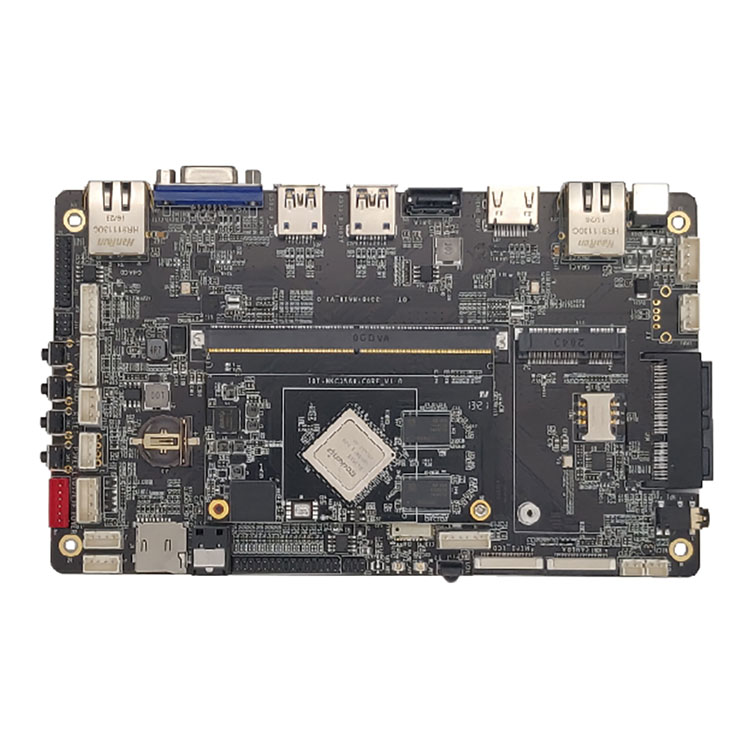

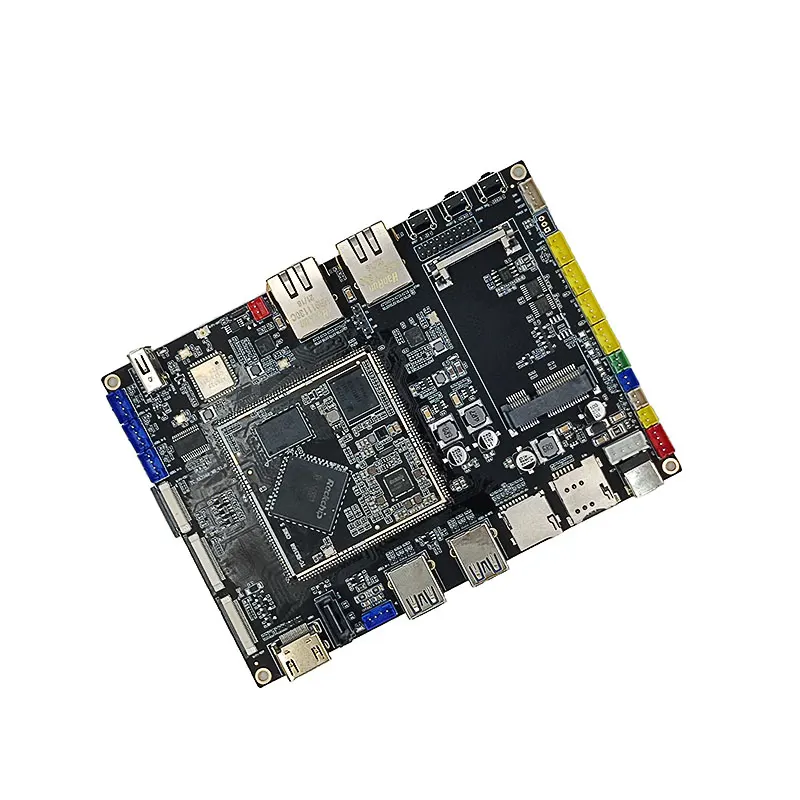

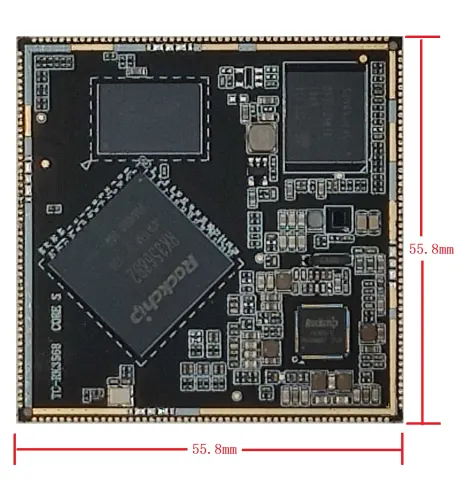

Apariencia de SOM

Frente SOM

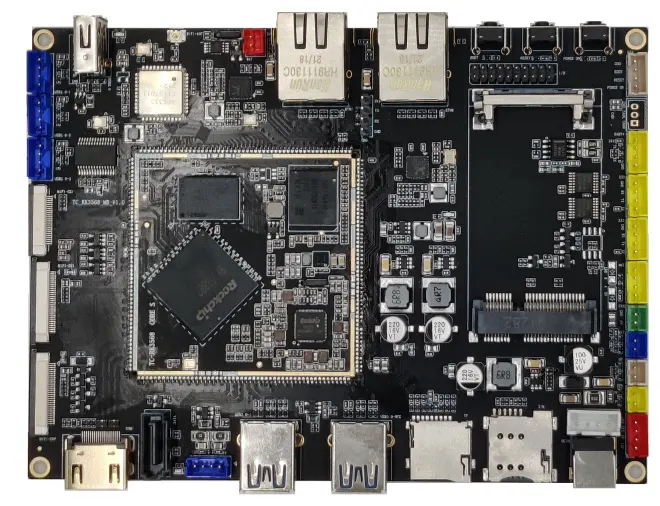

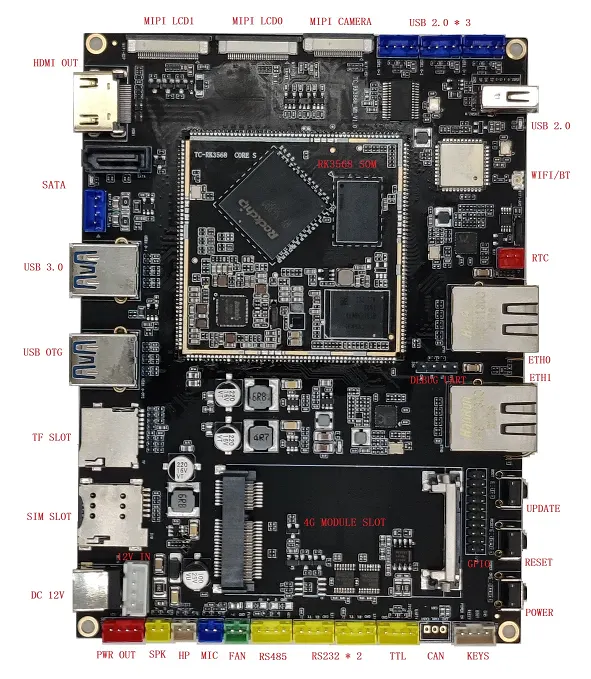

Apariencia de la placa de desarrollo

Capítulo 2. Definición de PIN de SOM

PIN SOM Definición

|

ALFILER |

Definición de pines de la placa base |

Función predeterminada |

Descripción de la función predeterminada |

Potencia de E/S |

Tipo de almohadilla IO pull |

|

1 |

VCC3V3_SYS |

Fuente de alimentación del sistema de 3,3 V |

Voltaje de entrada 3.3V |

|

- |

|

2 |

VCC3V3_SYS |

Fuente de alimentación del sistema de 3,3 V |

Voltaje de entrada 3.3V |

|

- |

|

3 |

TIERRA |

TIERRA |

TIERRA |

|

- |

|

4 |

TIERRA |

TIERRA |

TIERRA |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

Entrada de detección SDMMC0 |

3,3 V |

E/S ARRIBA |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

Puerto de datos SDMMC0 |

3,3 V |

E/S ARRIBA

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

Puerto de datos SDMMC0 |

3,3 V |

E/S ARRIBA

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

Puerto de datos SDMMC0 |

3,3 V |

E/S ARRIBA

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

Puerto de datos SDMMC0 |

3,3 V |

E/S ARRIBA

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

Salida de comando SDMMC0 |

3,3 V |

E/S ARRIBA

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

Salida de reloj SDMMC0

|

3,3 V |

E/S ABAJO |

|

12 |

RESTABLECER |

NPOR_U |

Detección de señal de reinicio |

3,3 V |

- |

|

13 |

RK809_PWRON |

Encendido |

Entrada de señal de encendido, tecla de encendido de conexión externa, bajo activo |

|

- |

|

14 |

RECUPERACIÓN |

SARADC_VIN0 |

Entrada de teclado AD |

1,8 V |

- |

|

15 |

EXT_ES |

EXT_ES |

Habilitación de energía PMIC |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Auricular directamente |

3,3 V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Auricular dejado fuera |

3,3 V |

- |

|

18 |

SPKP_SALIDA |

SPKP_SALIDA |

Hablar claro |

5 V/0,6 W |

- |

|

19 |

SPKN_SALIDA |

SPKN_SALIDA |

Hablar claro- |

5 V/0,6 W |

- |

|

20 |

MIC1_INN |

MIC1_POSADA/MIC_R |

MIC1_INN |

3,3 V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3,3 V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Detección de auriculares |

3,3 V |

E/S ABAJO |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3 V |

E/S ABAJO |

|

24 |

VCC3V3_SD |

Fuente de alimentación de 3,3 V |

Voltaje de salida 3,3 V para tarjeta SD, corriente de salida nominal 2A |

|

- |

|

25 |

VCC_3V3 |

Fuente de alimentación de 3,3 V |

Voltaje de salida 3,3 V, corriente de salida nominal 2A |

|

- |

|

26 |

VCC_1V8 |

Fuente de alimentación de 1,8 V |

Voltaje de salida 1,8 V, corriente de salida nominal 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3 V |

E/S ABAJO |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3 V |

E/S ABAJO |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3 V |

E/S ABAJO |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3 V |

E/S ABAJO |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0 transmitir datos |

1,8 V |

E/S ARRIBA |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0 transmitir datos |

1,8 V |

E/S ARRIBA |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0 transmitir datos |

1,8 V |

E/S ARRIBA |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0 transmitir datos |

1,8 V |

E/S ARRIBA |

|

35 |

GMAC0_TXEN |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

Habilitación de transmisión GMAC0 |

1,8 V |

E/S ARRIBA |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

Reloj de transmisión GMAC0 |

1,8 V |

E/S ABAJO |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 recibir datos |

1.8v |

E/S ARRIBA |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 recibir datos |

1,8 V |

E/S ABAJO |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 recibir datos |

1.8v |

E/S ARRIBA |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 recibir datos |

1,8 V |

E/S ARRIBA |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

Señal válida de datos GMAC0 RX |

1,8 V |

E/S ABAJO |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

Reloj de recepción GMAC0 |

1,8 V |

E/S ARRIBA |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25MHz CPU a PHY, NC predeterminado |

1,8 V |

E/S ABAJO |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

reloj externo GMAC0 |

1,8 V |

E/S ABAJO |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

Reloj de gestión MAC0 |

1,8 V |

E/S ABAJO |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

Comando y datos de gestión MAC0 |

1,8 V |

E/S ABAJO |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3 V |

E/S ABAJO |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3 V |

E/S ABAJO |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, bajo activo |

1,8 V |

E/S ABAJO |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

Puerto serie I2C 5 |

3,3 V |

E/S ABAJO |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

Puerto serie I2C 5 |

3,3 V |

E/S ABAJO |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3 V |

E/S ABAJO |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

Puede transmitir datos |

3,3 V |

E/S ABAJO |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

Puede recibir datos |

3,3 V |

E/S ABAJO |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

Puerto serie UART |

3,3 V |

E/S ARRIBA |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Transmisión de datos del puerto serie UART para depuración |

3,3 V |

E/S ARRIBA |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

Recepción de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

Transmisión de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

Transmisión de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

Recepción de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

Recepción de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

Transmisión de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

Recepción de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

Transmisión de datos del puerto marítimo UART |

3,3 V |

E/S ABAJO |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

Dirección de datos RS485 |

3,3 V |

E/S ABAJO |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3 V |

E/S ARRIBA |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3 V |

E/S ABAJO |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3 V |

E/S ABAJO |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3 V |

E/S ABAJO |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3 V |

E/S ABAJO |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3 V |

E/S ABAJO |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3 V |

E/S ABAJO |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3 V |

E/S ABAJO |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Habilitación de energía del módulo Bluetooth |

3,3 V |

E/S ABAJO |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

Recepción de datos del puerto marítimo UART |

1,8V |

E/S ABAJO |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

Transmisión de datos del puerto marítimo UART |

1,8 V |

E/S ABAJO |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8 V |

E/S ABAJO |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8 V |

E/S ABAJO |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

Habilitar WIFI_REG |

1,8 V |

E/S ABAJO |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

Anfitrión de activación WIFI |

1,8 V |

E/S ABAJO |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

reloj SDMMC2 |

1,8 V |

E/S ABAJO |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

Comando SDMMC2 |

1,8 V |

E/S ABAJO |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

datos SDMMC2 |

1,8 V |

E/S ABAJO |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

datos SDMMC2 |

1,8 V |

E/S ABAJO |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

datos SDMMC2 |

1,8 V |

E/S ABAJO |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

datos SDMMC2 |

1,8 V |

E/S ABAJO |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3 V |

E/S ABAJO |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3 V |

E/S ABAJO |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

Comando y datos de gestión de GMAC1 |

1,8 V |

E/S ABAJO |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

Reloj de gestión GMAC1 |

1,8 V |

E/S ABAJO |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

reloj externo GMAC1 |

1,8 V |

E/S ABAJO |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

Salida de reloj ETH1 |

1,8 V |

E/S ABAJO |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

Reloj de recepción GMAC1 |

1,8 V |

E/S ABAJO |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

Señal válida de datos GMAC1 RX |

1,8 V |

E/S ABAJO |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 recibir datos |

1,8 V |

E/S ABAJO |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 recibir datos |

1,8 V |

E/S ABAJO |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 recibir datos |

1,8 V |

E/S ABAJO |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 recibir datos |

1,8 V |

E/S ABAJO |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

Reloj de transmisión GMAC1 |

1,8 V |

E/S ABAJO |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

Habilitación de transmisión GMAC1 |

1,8 V |

E/S ABAJO |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 transmite datos |

1,8 V |

E/S ABAJO |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 transmite datos |

1,8 V |

E/S ABAJO |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 transmite datos |

1,8 V |

E/S ABAJO |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 transmite datos |

1,8 V |

E/S ABAJO |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Restablecimiento del panel táctil |

3,3 V |

E/S ARRIBA

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Entrada de datos de interrupción del panel táctil |

3,3 V |

E/S ARRIBA |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

Puerto serie I2C 1 |

3,3 V |

E/S ARRIBA |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

Puerto serie I2C 1 |

3,3 V |

E/S ARRIBA |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

Puerto serie I2C 3 |

3,3 V |

E/S ARRIBA |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

Puerto serie I2C 3 |

3,3 V |

E/S ARRIBA |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

Puerto serie I2C 2 |

1,8 V |

E/S ABAJO |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

Puerto serie I2C 2 |

1,8 V |

E/S ABAJO |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Apagado de la cámara 1 |

3,3 V |

E/S ABAJO |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Restablecimiento de la cámara 1 |

3,3 V |

E/S ABAJO |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Restablecimiento de la cámara 0 |

3,3 V |

E/S ABAJO |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Apagado de la cámara 0 |

3,3 V |

E/S ABAJO |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3 V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3 V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3 V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3 V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Salida de reloj para cámara. |

3,3 V |

E/S ABAJO |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

reloj de salida CIF |

1,8 V |

E/S ABAJO |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8 V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8 V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8 V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8 V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8 V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8 V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8 V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8 V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8 V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8 V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8 V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8 V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

Habilitación de energía LCD |

3,3 V |

E/S ABAJO |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

retroiluminación LCD PWM |

3,3 V |

E/S ABAJO |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

retroiluminación LCD PWM |

3,3 V |

E/S ABAJO |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

Habilitación de energía LCD |

3,3 V |

E/S ABAJO |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8 V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8 V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8 V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8 V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8 V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8 V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8 V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8 V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8 V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8 V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT y resistencia en serie 2.2R |

1,8 V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Puerto serie I2C para HDMI |

3,3 V |

E/S ARRIBA |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Puerto serie I2C para HDMI |

3,3 V |

E/S ARRIBA |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3 V |

E/S ARRIBA |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

Conexión en caliente HDMI_TX |

1,8 V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

E/S ABAJO |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3 V |

E/S ABAJO |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

Restablecer PCIE30X2 |

3,3 V |

E/S ABAJO |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

Host de activación PCIE30X2 |

3,3 V |

E/S ABAJO |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

Habilitación de energía PCIE |

1,8 V |

E/S ABAJO |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8 V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8 V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8 V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8 V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8 V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8 V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8 V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8 V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8 V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8 V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8 V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8 V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8 V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8 V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8 V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8 V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA activo indicar |

3,3 V |

E/S ABAJO |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8 V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8 V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8 V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8 V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3 V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3 V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8 V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8 V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8 V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8 V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3 V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3 V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3 V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUS detectar |

3,3 V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

Habilitación de alimentación de host USB |

3,3 V |

E/S ABAJO |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

Activación de alimentación USB OTG |

3,3 V |

E/S ABAJO |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8 V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8 V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8 V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1.8v |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8 V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8 V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8 V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8 V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8 V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8 V |

- |

Capítulo 3. Junta de Desarrollo

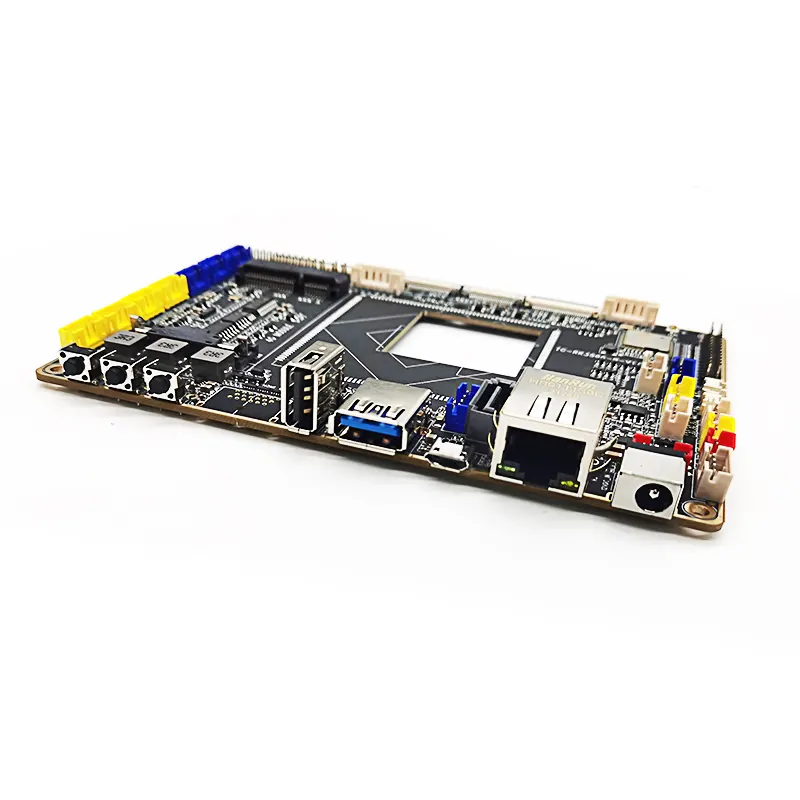

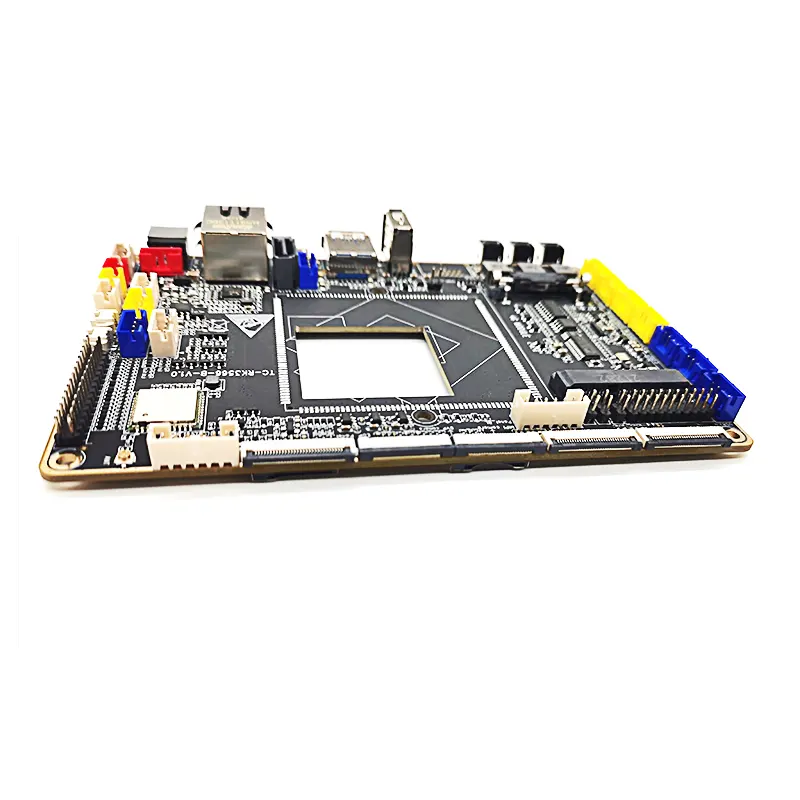

Tamaño

El tamaño es de 150 mm * 110 mm, 4 capas, 1,6 mm de espesor.

Descripción de las interfaces

|

Descripción de las interfaces |

|

|

NO. |

Nombre |

|

ã1ã |

Entrada de 12 V CC/entrada de 4 pines de 2,54 mm y 12 V |

|

ã2ã |

Ranura para tarjeta SIM del módulo 4G |

|

ã3ã |

Ranura para tarjetas TF |

|

ã4ã |

USB OTG |

|

ã5ã |

ANFITRIÓN USB3.0 |

|

ã6ã |

Datos SATA |

|

ã7ã |

Salida HDMI |

|

ã8ã |

MIPILCD1 |

|

ã9ã |

MIPILCD0 |

|

ã10ã |

Cámara MIPI |

|

ã11ã |

USB2.0 * 3 |

|

ã12ã |

USB 2.0 tipo A |

|

ã13ã |

Wi-Fi/BT (AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Actualizar clave |

|

ã18ã |

Tecla de reinicio |

|

ã19ã |

Tecla de encendido |

|

ã20ã |

Teclas (4 pines 2,0 mm) |

|

ã21ã |

PUEDE (3 pines 2,0 mm) |

|

ã22ã |

Uart TTL (4 pines 2,0 mm) |

|

ã23ã |

RS232 * 2 (4 pines 2,0 mm) |

|

ã24ã |

RS485 (4 pines 2,0 mm) |

|

ã25ã |

VENTILADOR (2 pines 2,0 mm) |

|

ã26ã |

MICRÓFONO (2 pines 2,0 mm) |

|

ã27ã |

HP (2 pines 2,0 mm) |

|

ã28ã |

SPK (2 pines 2,0 mm) |

|

ã29ã |

Salida de alimentación (4 pines 2,0 mm) |

|

ã30ã |

Uart de depuración (4 pines 2,0 mm) |

|

ã31ã |

GPIO (2*10 pines 2,0 mm) |

|

ã32ã |

Ranura para módulo 4G (puerto PCIE) |

|

ã33ã |

RK3568 SOM |

La placa utiliza una fuente de alimentación de 12 V CC, que se conecta mediante un conector de entrada de 12 V CC o un conector de entrada de 4 pines de 2,54 mm y 12 V.

Los detalles de otras interfaces podrían referirse al diagrama esquemático y al diseño de la placa de desarrollo.

Capítulo 4. Diseño de hardware

Referencia de diseño

Tome la placa de desarrollo TC-RK3568 como plataforma de hardware, puede consultar el diseño de alimentación, el diseño de USB, el diseño de puerto PCIE, el diseño de pantalla MIPI, el diseño de audio, el diseño de Ethernet, el diseño de cámara, etc. Estos están abiertos a los clientes, pueden referirse a nuestro diseño de placa portadora.

Capítulo 5. Diseño de software

La plataforma de desarrollo TC-RK3568 es compatible con Android11, Linux Buildroot, Ubuntu y Debian System OS, los códigos fuente están abiertos. Puede leer referencias como el manual de usuario del sistema Thinkcore TC-RK3568.